# Efficient Approximate Adder Architecture for Error Tolerant Applications with use of new logic values

Prashant Sharma<sup>1</sup> and Sudha Nair<sup>2</sup>

<sup>1</sup>Research scholar,<sup>2</sup>Assistant Professor, Electronics and Comm. dept., RKDF- IST, Bhopal, India

### -----ABSTRACT-----

Ultra-high energy efficiency is required for all the battery operated devices due to increased functionality on the single chip. In conventional digital VLSI design, it is assumed that a circuit/system should function perfectly to provide accurate results. There are many applications which can tolerate small amount of error in their processing e.g. image/video processing, commonly called error tolerant applications. For many digital systems, the data already contained errors. The proposed adder can be efficiently utilized in the image video processing applications. In order to evaluate the efficacy of the proposed adder, proposed and existing adder architecture is implemented on MATLAB to evaluate error metrics and Tanner to evaluate design metrics. Simulation results shows that proposed adder significantly reduces power, area and delay at small loss in accuracy.

Key Word:- VLSI, MATLAB, Image processing, Adder, Highspeed integrated circuits

Date of Submission: 17 July 2015 Date of Accepted: 05 August 2015

# I. INTRODUCTION

Leveraging the applications having error tolerance, we can design adder which provide approximate result very fast compered to conventional design.Small loss in accuracy provides tremendous improvement in power, delay and area. Error Tolerant Adder (ETA) provides high speed by cutting down the carry propagation.ETA can be used in application, which need high speed and may tolerate small error.

# Error Tolerant Adder (ETA)

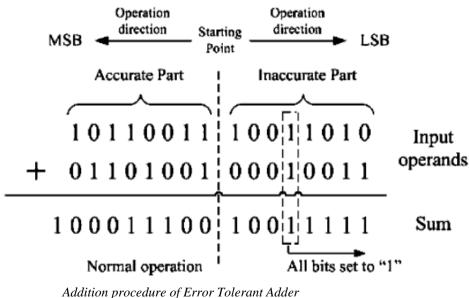

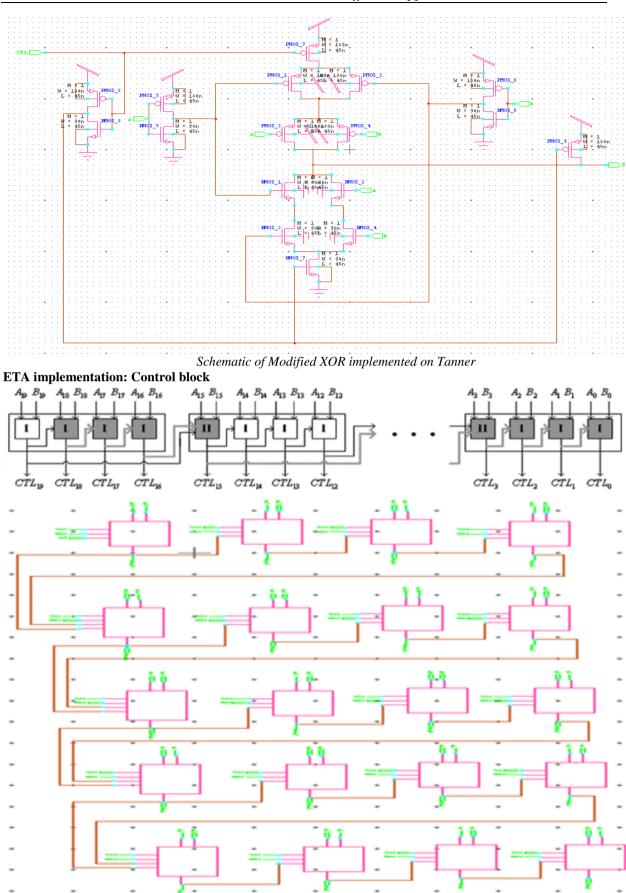

The principle of ETA is to divide adder into: Accurate and Inaccurate partAccurate part includes higher order bits and the inaccurate part includes remaining lower order bits. The addition process starts from the joining point towards the two opposite directions simultaneously

Error Tolerant Adder (cont...)

To minimize the overall error due to the elimination of the carry chain, a special strategy is adapted Check every bit position from left to right, If both input bits are "0" or different, normal one-bit addition is performed and the

operation proceeds to next bit position, If both input bits are "1", the checking process stopped and from this bit onwards, all sum bits to the right are set to "1".

#### nion procedure of Error Tolerani Adde

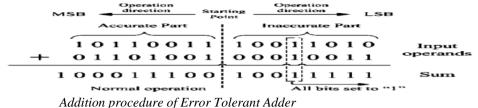

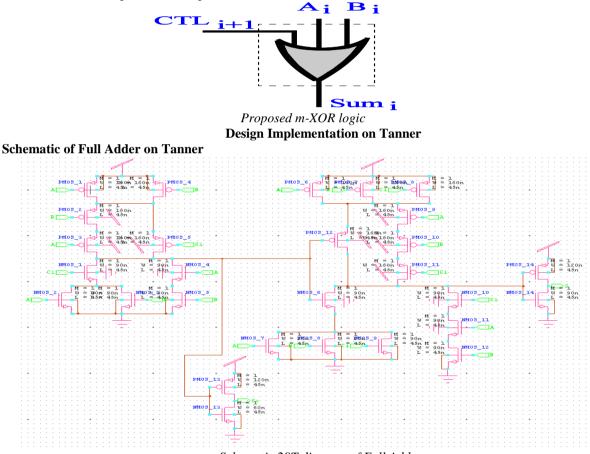

# **Proposed Addition Logic**

The existing ETA requires large number of transistor to implement approximate sum which in turn increases power consumption. The same functionality can be achieved by the proposed circuit as shown belowThis circuit significantly reduces transistor count (17 in the ETA whereas 8 in the proposed logic i.e. 52.9% reduction) which in turn reduces power consumption.

Schematic 28T diagram of Full Adder

# Result

## **Design Metrics Comparison: 8-bit Adders**

| Type of Adder | Power (uw) | Delay (ns) | PDP (fJ) | Transistor<br>Count |

|---------------|------------|------------|----------|---------------------|

| ЕТА           | 1.85       | 0.134      | 0.247    | 222                 |

## **Design Metrics Comparison: 16-bit Adders**

| Type of Adder | Power (uw) | Delay (ns) | PDP (fJ) | Transistor<br>Count |

|---------------|------------|------------|----------|---------------------|

| ETA           | 2.56       | 0.305      | 0.78     | 542                 |

## **Design Metrics Comparison: 32-bit**

| Type of Adder | Power (uw) | Delay (ns) | PDP (fJ) | Transistor<br>Count |

|---------------|------------|------------|----------|---------------------|

| ETA           | 5.18       | 0.616      | 3.19     | 912                 |

# Conclusion

Approximate adder in these application significantly improves the design metrics at the cost slightly degradation in quality.Simulation results on the Tanner shows that ETA exhibits significant improvement over the accurate adder architectures.MATLAB simulation results shows very small amount of error.Thus ETA can be effectively applied in the image/video processing applications

## Reference

- [1]. International Technology Roadmap for Semiconductors [Online]. Available: <u>http://public.itrs.net/</u>

- [2]. B. Melvin and Z. Haiyang, "Error-tolerance and multi-media," in *Proc. 2006 Int. Conf. Intell. Inf. Hiding and Multimedia Signal Process.*, 2006, pp. 521–524.

- [3]. M. A. Breuer, S. K. Gupta, and T. M. Mak, "Design and error-tolerance in the presence of massive numbers of defects," *IEEE Des. Test Comput.*, vol. 24, no. 3, pp. 216–227, May-Jun. 2004.

- [4]. M. A. Breuer, "Intelligible test techniques to support error-tolerance," in *Proc. Asian Test Symp., Nov. 2004, pp. 386–393.*[5]. K. J. Lee, T. Y. Hsieh, and M. A. Breuer, "A novel testing methodology based on error-rate to support error-tolerance," in *Proc.*

- [5]. K. J. Lee, T. Y. Hsieh, and M. A. Breuer, "A novel testing methodology based on error-rate to support error-tolerance," in *Proc. Int. Test Conf.*, 2005, pp. 1136–1144.

- [6]. S. Chong and A. Ortega, "Hardware testing for error tolerant multimedia compression based on linear transforms," in Proc. Defect and Fault Tolerance in VLSI Syst. Symp., 2005, pp. 523–531.

- [7]. V. Palem, "Energy aware computing through probabilistic switching: A study of limits," *IEEE Trans. Comput., vol. 54, no. 9, pp.* 1123–1137, Sep. 2005.

- [8]. Cheemalavagu, P. Korkmaz, and K. V. Palem, "Ultra low energy computing via probabilistic algorithms and devices: CMOS device primitives and the energy-probability relationship," in *Proc. 2004 Int. Conf. Solid State Devices and Materials, Tokyo, Japan, Sep. 2004, pp.* 402–403