# Comparative Analysis of low area and low power D Flip-Flop for Different Logic Values

# Nitin Kumar Singh Chauhan, Anshul Jain

Sri Ram College of Engineering and Management Banmore Near Gwalior (M.P.)

-----ABSTRACT-----

In this paper we propose to increase the performance of flip flops a set of rule for consistent estimation of the performance and power features of the flip flop. A new simulation and optimization approach is presented triggering both high performance and power budget issue. The analysis approach revels the source of performance and power consumption bottlenecks in different design styles. Certain misleading parameters have been properly modified and the flip flop analysis on the bases of performance

KEYWORDS:- flip flops, optimization approach, power consumption bottlenecks

| Date of Submission: 17 July 2014 | Date of Publication: 05 August 2014 |

|----------------------------------|-------------------------------------|

|                                  | <br>                                |

## I. INTRODUCTION

With an increasing demand for higher performance and lower power dissipation in current microprocessor, new circuit design techniques are needed for both switching logic and storage devices. In a digital system, flip-flops are often thought of as memory devices, whose primary function is to store state information and data results. *As* complexity in microprocessor increases, both logic requirements and storage depth Swill also increase. This will lead to a larger number of flip-flops and may result in larger power consumption. In fact, the maximum speed of a flip-flop is directly proportional to the total power dissipated. In the mobile part used in today's computer notebooks, emphasis on power dissipation has been a major primarily design concern.

One way for a system to save power is to enter a sleep mode where the states of the logic remain saved until the system becomes active again. This is achieved by turning off the clock and forcing the system into a standby state. Once the system enters this state, the storage

capacitance may leak over time resulting in a loss of stored information. To maintain the capacitive charge during sleep mode, a positive feedback inverter or level restorer is required. Such configurations are considered to be a pseudo-static design; a dynamic CMOS latch with feedback that refreshes itself to retain the stored content. The high gain from the cross-coupling inverter makes pseudo-static flip-flop ideally as signal driver. When the system revives into its normal state, the control logic reinitializes and continues where it last left off.

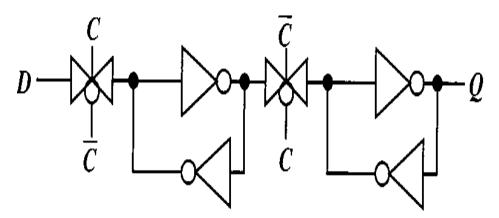

## 3.3.2 Low Area D-FF

#### **II. ANALYSIS AND SIMULATION**

A common approach for reducing area overhead of the conventional DFF is to remove the two feedback transmission gates. This low-area DFF is depicted in Fig. 1(b). Although the strength of feedback inverters has been weakened to minimize short-circuit power dissipation due to voltage contention, this low-area DFF still consumes 18% more total power and is 42% slower (or has 76% more energy) compared to the conventional DFF.

Comparative Analysis of low area and low power....

Schematic of low power D-FF

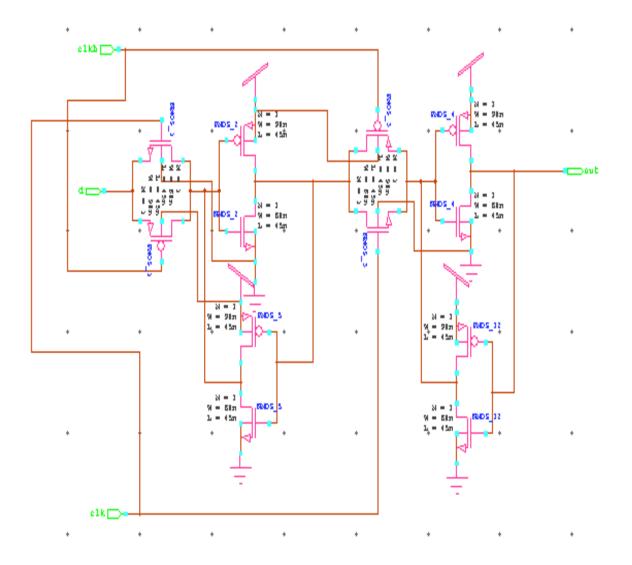

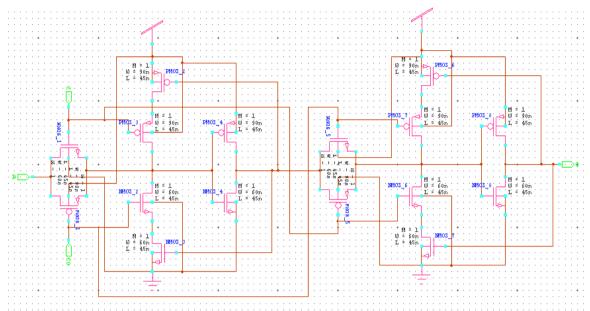

schematic of low area D-flip-flop using tanner tool

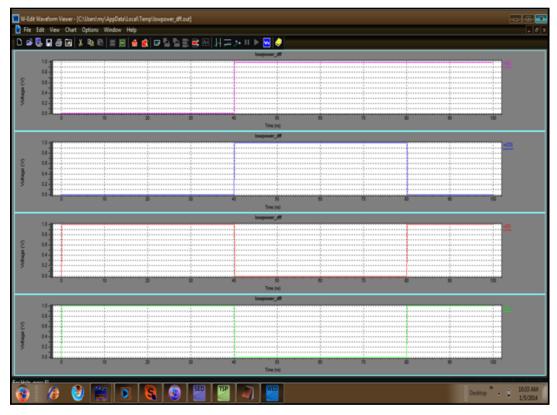

Figure Simulation result of low area D flip flop

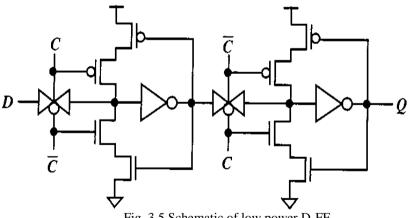

#### Low-Power D-FF

One approach to optimize for power dissipation is to replace the inverter and transmission gate in the feedback path of conventional D-FF with a single tri-state inverter. This approach is referred to as a low-power DFF.

Fig. 3.5 Schematic of low power D-FF

Schematic of Low Power D-FF using Tanner tool

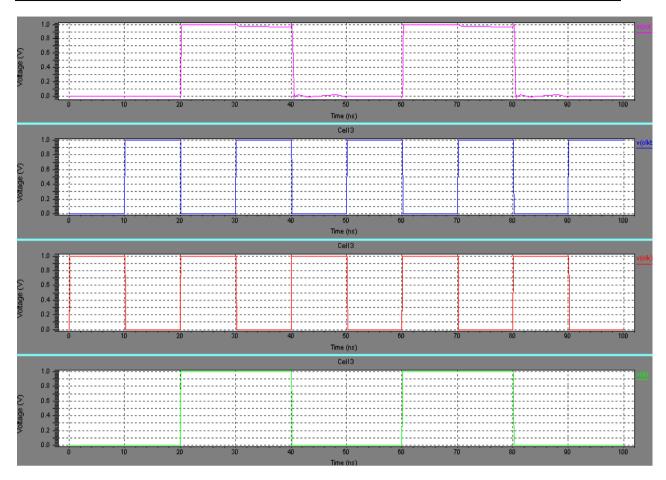

Simulation result of low power D flip flop

# **III. RESULTS & DISCUSSION**

In this thesis various types of D-FF are designed and simulated using TANNER tool. The Simulation results in the tables given below. Tanner 14.1 tool schematic editor is used to draw schematic of the D-FF. Schematic of these flip-flops are firstly designed on tanner's schematic editor and net lists of the circuits are than taken out. These net lists run with 45 nm Predictive Technology Model (PTM) file on tanner's spice simulator to get simulation results. Various D-flip flops are designed and simulated on different power supply like 0.8V ,1 V and 1.2 V and than their results has been compared on the basis of number of transistors, power consumption and Delay

| Power analysis of Low j | power D flip flop is as |       |      |  |

|-------------------------|-------------------------|-------|------|--|

| Supply voltage          | 0.8 V                   | 1.0 V | 1.2V |  |

| 11.5 8                  |                         |       |      |  |

|                         |                         |       |      |  |

| Dower (N. wett)         | 0.71                    | 1.042 | 1.14 |  |

| Power (N-watt)          | 0.71                    | 1.042 | 1.14 |  |

|                         |                         |       |      |  |

|                         |                         |       |      |  |

|                         |                         |       |      |  |

#### Power analysis of low area D flip flop is as

.....

| Supply voltage          | 0.8 V                  | 1.0 V  | 1.2V   |

|-------------------------|------------------------|--------|--------|

| Power (N-watt)          | 1.57                   | 1.69   | 1.719  |

| Delay analysis of Low p | <u> </u>               |        |        |

| Supply voltage          | 0.8 V                  | 1.0 V  | 1.2V   |

| Delay (N-Sec.)          | 2.001                  | 2.0035 | 2.0050 |

| Delay analysis of Low A | Area D flip flop is as |        |        |

| Supply voltage          | 0.8 V                  | 1.0 V  | 1.2V   |

|                         |                        |        |        |

| Delay (N-Sec.)          | 1.816                  | 1.808  | 1.7911 |

#### **IV. CONCLUSION**

Sequential circuits required different types of memory elements some of them required fast speed and some of them required low power and low area thus in this work a comparative analysis of different D flip flop is done which concluded that some D flip flop is fastest in speed and someone consumes less power for designing optimized value of PDP (power delay product) has been calculated.

#### REFERNCES

- S. H. Unger and C. Tan, "Clocking schemes for high-speed digital systems," IEEE Trans. Comput., vol. C-35, pp 880-895, Oct. 1986.

- [2]. Fred U. Rosenberger and Charles E. Molnar, "Comments on Metastability of CMOS Latch/Flip-Flop," IEEE Journal ofSolid-State Circuits, vol. 27, no.14 pp. 128-130, January 1992.

[3]. C.L. Portmann and T. H. Y. Meng, "Metastability in CMOS Library Elements in Reduced Supply and Technology Scaled Applications," IEEE Journal ofSolidState Circuits, vol. 30, no. 1 pp. 39-46, January 1995.

- [4]. Vladimir Stojanovic and Vojin G. Oklobdzija, "Comparative Analysis of MasterSlave Latches and Flip-Flops for High-Performance and Low-Power Systems," IEEE Journal ofSolid-State Circuits, vol. 34, no. 4 pp. 536-548, April1999.

- [5]. Lee-Sup Kim and Robert W. Dutton, "Metastability of CMOS Latch/Flip-Flop," IEEE Journal ofSolid-State Circuits, vol. 25, no. 4 pp. 942-951, August 1990.

[6]. Uming Ko and Poras T. Balsara, "High Performance, Energy Efficient D Flip-flop Circuits," September 1998.

[7]. Kenneth L. Shepard and Vinod Narayanan, "Conquering Noise in Deep-Submicron Digital ICs," IEEE Design and Test of Computers, pp 51-62, January-March 1998..

- [9]. Fred Rosenberger and Thomas J. Chaney, "Flip-Flop Resolving Time Test Circuit," IEEE Journal ofSolid-State Circuits, vol. SC-17, no. 4 pp. 731-738, August 1982.

- [10]. L. R. Marino, "General Theory of Metastable Operation," IEEE Trans. Computers, vol. C-30, pp. 107-115, Feb. 1981.

<sup>[8].</sup> David Harris and Mark A Horowitz, "Skew-Tolerant Domino Circuits," IEEE Journal ofSolid-State Circuits, vol. 32, no. 11 pp. 1702-1711, November 1997.